# **IRPLDIM3**

# IRPLDIM3 Wide Range Input Linear Dimming Fluorescent Ballast using the IRS2158D

# **Table of Contents**

|                                                          | Page |

|----------------------------------------------------------|------|

| 1. Features                                              | 2    |

| 2. Description                                           | 2    |

| 3. Electrical Characteristics                            | 3    |

| 4. Fault Protection Characteristics                      | 3    |

| 5. IRPLDIM3 Schematics                                   | 4    |

| 6. PCB Component Placement Diagram and Board Fabrication | 5    |

| 7. Bill of Material and Inductor Specification           | 8    |

| 8. Functional Description                                | 13   |

www.irf.com - 1 -

#### 1. Features

- Drives 1 x 28W TL5 Lamp

- Input Voltage: 90-305Vac

- High Power Factor/Low THD

- High Frequency Operation

- Lamp Filament Preheating

- Lamp Fault Protection with Auto-Restart

- Low AC Line/Brownout Protection

- End of Lamp Life Shutdown

- IRS2158D HVIC Ballast Controller

### 2. Description

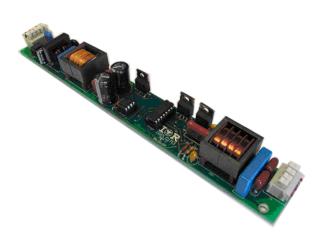

The IRPLDIM3 reference design kit consists of a high power factor wide input voltage range dimming Fluorescent ballast, with a fully isolated 0 to 10V control interface, driving a single T5 28 W rapid start linear lamp. The design contains an EMI filter, active power factor correction and a dimming ballast control circuit using the PDIP16 version of <a href="IRS2158D">IRS2158D</a>. This demo board is intended to help with the evaluation of the IRS2158D dimming ballast control IC, demonstrate PCB layout techniques and serve as an aid in the development of production ballasts using the IRS2158D

Fig 1. IRPLDIM3 Block Diagram

www.irf.com - 2 -

# 3. Electrical Characteristics

| Parameter              | Units  | Value           |

|------------------------|--------|-----------------|

| Lamp Type              |        | 28W TL5         |

| Input Power            | [W]    | 30              |

| Lamp running voltage   | [Vpp]  | 600             |

| Run Mode Frequency     | [kHz]  | 50              |

| Preheat Mode Frequency | [kHz]  | 56              |

| Preheat Time           | [s]    | 1.0             |

| Lamp Preheat Voltage   | [Vpp]  | 600             |

| Lamp Ignition Voltage  | [kVpp] | 2.0             |

| Input AC Voltage Range | [VAC]  | 90-305VAC       |

| Power Factor           |        | 0.995 at 120VAC |

| TOWEL PACIOL           |        | 0.98 at 220 VAC |

# 4. Fault Protection Characteristics

| Fault                 | Protection                               | Ballast     | Restart Operation     |

|-----------------------|------------------------------------------|-------------|-----------------------|

| Brown-out             | VDC Brown-out detect                     | Shutdown    | Line voltage increase |

| Upper filament broken | CS Over Current detect                   | Deactivates | Lamp exchange         |

| Lower filament broken | SD Open filament detect on SD/EOL pin    | Deactivates | Lamp exchange         |

| Failure to ignite     | CS Ignition detection timeout            | Deactivates | Lamp exchange         |

| No lamp               | SD Open filament detect on SD/EOL pin    | Deactivates | Lamp inserted         |

| End of life           | EOL lamp voltage detection on SD/EOL pin | Deactivates | Lamp exchange         |

<u>www.irf.com</u>

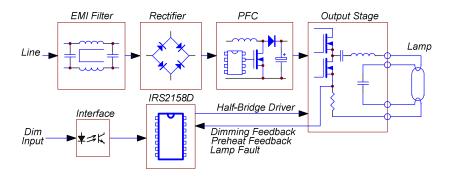

# 5. IRPLDIM3 Schematics

Fig. 2: Schematic Diagram, IRS2158D, Single Lamp, Voltage Mode Heating

www.irf.com - 4 -

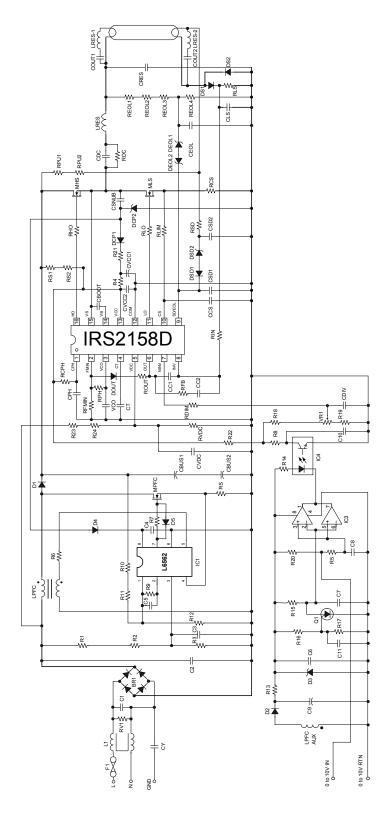

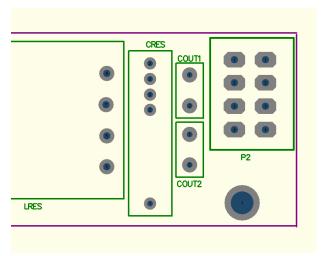

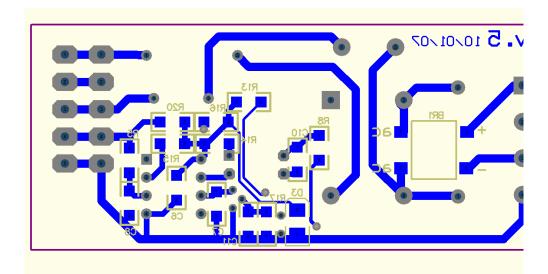

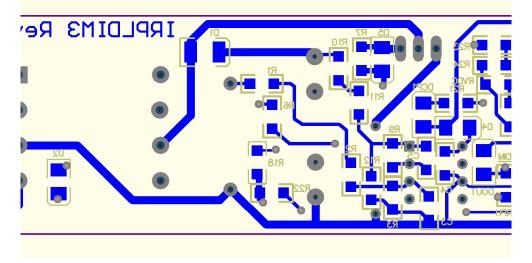

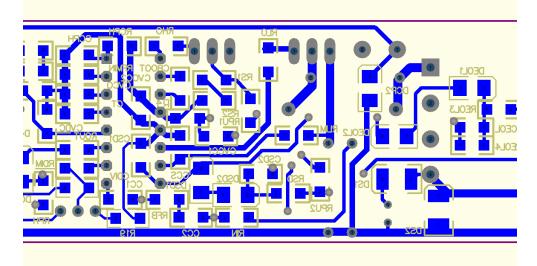

# 6. PCB Component Placement Diagram and Board Fabrication

<u>www.irf.com</u>

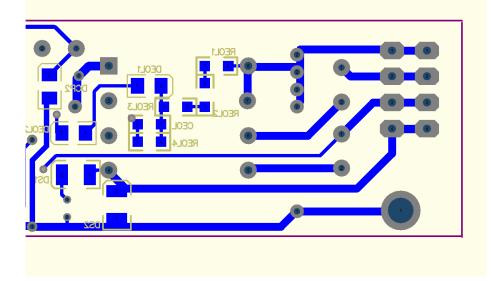

Top Layers

<u>www.irf.com</u>

**Bottom Layers**

Fig. 3: PCB Component Placement Diagram

<u>www.irf.com</u> - 7 -

# 7. Bill of Material and Inductor Specification

| Item# | Qty | Manufacturer            | Part Number    | Description                     | Reference                          |

|-------|-----|-------------------------|----------------|---------------------------------|------------------------------------|

| 1     | 1   | ST Microelectronics     | L6562N         | PFC Control IC                  | IC1                                |

| 2     | 1   | International Rectifier | IRS2158D       | Ballast Control IC              | IC2                                |

| 3     | 1   | ST Microelectronics     | LM393N         | Dual Comparator IC              | IC3                                |

| 4     | 1   | Panasonic               | CNC1S101       | Opto Isolator                   | IC4                                |

| 5     | 1   | ON Semiconductor        | 2N6027RLRAG    | Programmable                    | Q1                                 |

|       |     |                         |                | Unijunction                     |                                    |

|       |     |                         |                | Transistor                      |                                    |

| 6     | 3   | International Rectifier | IRFBC30        | N-MOSFET                        | MPFC, MHS, MLS                     |

| 7     | 1   | Fairchild Semiconductor | DF10S          | Bridge Rectifier                | BR1                                |

| 8     | 6   | Diodes Inc              | LL4148-13      | Diode                           | DCP1, DOUT,<br>DSD1, D2, D4, D5    |

| 9     | 1   | Diodes Inc              | ZMM5236B-7     | Zener Diode 7V5                 | DEOL1                              |

| 10    | 1   | Diodes Inc              | ZMM5231B-7     | Zener Diode 5V1                 | DEOL2                              |

| 11    | 2   | Diodes Inc              | ZMM5248B-7     | Zener Diode 18V                 | D3, DCP2                           |

|       | 1   | Diodes Inc              | ZMM5242B-7     | Zener Diode 12V                 | DSD2                               |

| 12    | 3   | Diodes Inc              | US1J-13-F      | Diode                           | DS1, DS2, D1                       |

| 13    | 1   | Panasonic-ECG           | ELF-15N007A    | Common mode<br>Choke            | L1                                 |

| 14    | 1   | Vogt Electronics        | IL 070 118 11  | PFC Inductor                    | LPFC                               |

| 15    | 1   | Vogt Electronics        | IL 070 118 21  | Resonant Inductor               | LRES                               |

| 16    | 1   | Epcos                   | B32922A2224M   | Capacitor 220 nF, 305VAC        | C1                                 |

| 17    | 1   | BC Components           | 2222 338 14104 | Capacitor 100 nF,<br>440V       | C2                                 |

| 18    | 1   | Panasonic-ECG           | ECU-V1H103KBM  | Capacitor 10n, 50V, 1206        | C3                                 |

| 19    | 2   | Panasonic-ECG           | ECJ-3YX1C106K  | Capacitor 10u, 16V, 1206        | C4, C6                             |

| 20    | 1   | Panasonic-ECG           | ECJ-3VB1C684K  | Capacitor 0.68 μF,<br>16V, 1206 | C5                                 |

| 21    | 5   | Panasonic-ECG           | ECJ-3VB1C104K  | Capacitor 100n, 16V, 1206       | C11, CBOOT,<br>CC2, CSD2,<br>CVCC2 |

| 22    | 1   | Panasonic-ECG           | ECU-V1H333KBM  | Capacitor 33nF, 50V, 1206       | C7                                 |

| 23    | 3   | Panasonic-ECG           | ECJ-3YB1C105K  | Capacitor 1 μF, 16V, 1206       | C8, CDIV, CVDC                     |

| 24    | 2   | Panasonic-ECG           | ECA-2EHG330    | Capacitor, 33 μF, 250V, 105C    | CBUS1, CBUS2                       |

| 25    | 1   | Panasonic-ECG           | ECJ-3YB1C225K  | Capacitor 2.2 μF,<br>16V, 1206  | CVCC1                              |

| 26    | 1   | Panasonic-ECG           | EEU-FC1H470    | Capacitor 47 μF,<br>50V, 105C   | C9                                 |

| 27    | 1   | Panasonic-ECG           | ECU-V1H471KBM  | Capacitor, 470 pF, 50V, 1206    | CCS                                |

| 28    | 1   | Panasonic-ECG           | ECQ-E6104KF    | Capacitor, 100 nF, 630V         | CDC                                |

| 29    | 3   | Panasonic-ECG           | ECJ-3VB1C474K  | Capacitor, 0.47 μF, 16V, 1206   | CEOL, CSD1,<br>CCPH                |

<u>www.irf.com</u> - 8 -

| CCIII |   |               |                         |                                     |                                   |

|-------|---|---------------|-------------------------|-------------------------------------|-----------------------------------|

| 30    | 1 | Kemet         | T356D226K006AS          | Capacitor, 22 μF, 6.3V, Tantalum    | CLS                               |

| 31    | 2 | Panasonic-ECG | ECQ-P1H333FZW           | Capacitor, 33 nF, 50V, Radial       | COUT1, COUT2                      |

| 32    | 1 | Panasonic-ECG | ECW-H16332HL            | Capacitor, 3.3 nF, 1600V            | CRES                              |

| 33    | 1 | Panasonic-ECG | ECK-A3A102KBP           | Capacitor, 1 nF,<br>1 kV, Radial    | CSNUB                             |

| 34    | 2 | Panasonic-ECG | ECJ-3YC2D102J           | Capacitor, 1 nF,<br>200V, 1206, NPO | CT, C10                           |

| 35    | 1 | Panasonic-ECG | ECJ-3YB2A223K           | Capacitor, 22 nF, 100V, 1206        | CVCO                              |

| 36    | 1 | Panasonic-ECG | ECJ-3VC2A222J           | Capacitor, 2.2 nF, 100V, 1206, NPO  | CC1                               |

| 37    | 1 | TDK           | CS13-<br>E2GA332MYGS    | Capacitor, 3.3 nF, Y                | CY                                |

| 38    | 2 | Panasonic-ECG | ERJ-P08J684V            | Resistor, 680 kΩ,<br>0.25W, 1206    | R1, R2                            |

| 39    | 1 | Panasonic-ECG | ERJ-8ENF7501V           | Resistor, 7.5 kΩ,<br>0.25W, 1206    | R3                                |

| 40    | 2 | Panasonic-ECG | ERJ-P08J223V            | Resistor, 22 kΩ,<br>0.25W, 1206     | R6, R19                           |

| 41    | 2 | Panasonic-ECG | ERJ-P08J150V            | Resistor, 15 Ω,<br>0.25W, 1206      | RLO, RHO                          |

| 42    | 3 | Panasonic-ECG | ERJ-P08J104V            | Resistor, 100 kΩ,<br>0.25W, 1206    | R9, R20, RSD                      |

| 43    | 2 | Panasonic-ECG | ERJ-P08J824V            | Resistor, 820 kΩ,<br>0.25W, 1206    | R10, R11                          |

| 44    | 1 | Panasonic-ECG | ERJ-P08J912V            | Resistor, 9.1 kΩ,<br>0.25W, 1206    | R12                               |

| 45    | 1 | Panasonic-ECG | ERJ-8ENF1001V           | Resistor, 1 kΩ,<br>0.25W, 1206      | RLIM                              |

| 46    | 1 | Panasonic-ECG | ERJ-P08J472V            | Resistor, 4.7 kΩ,<br>0.25W, 1206    | R14                               |

| 47    | 6 | Panasonic-ECG | ERJ-8ENF1002V           | Resistor, 10 kΩ,<br>0.25W, 1206     | R16, R17, RDIM,<br>RFB, RIN, ROUT |

| 48    | 1 | Panasonic-ECG | ERJ-P08J334V            | Resistor, 330 kΩ,<br>0.25W, 1206    | R18                               |

| 49    | 2 | Panasonic-ECG | ERJ-P08J100V            | Resistor, 10 Ω,<br>0.25W, 1206      | R4, R21                           |

| 50    | 2 | Panasonic-ECG | ERJ-P08J153V            | Resistor, 15 kΩ,<br>0.25W, 1206     | R22, RFMIN                        |

| 51    | 3 | Panasonic-ECG | ERJ-P08J105V            | Resistor, 1 MΩ,<br>0.25W, 1206      | RCPH, RPU1,<br>RPU2               |

| 52    | 2 | BC Components | 5073NW1R500J12A<br>FXBC | Resistor, 1.5 $\Omega$ , 1W, Axial  | RCS, RS                           |

| 53    | 1 | Panasonic-ECG | ERJ-P08J433V            | Resistor, 43 kΩ,<br>0.25W, 1206     | RVDC                              |

| 54    | 4 | Panasonic-ECG | ERJ-P08J224V            | Resistor, 220 kΩ,<br>0.25W, 1206    | REOL1, REOL2,<br>REOL3, R15       |

| 55    | 1 | Panasonic-ECG | ERJ-P08J203V            | Resistor, 20 kΩ,<br>0.25W, 1206     | REOL4                             |

| 56    | 1 | Panasonic-ECG | ERJ-P08J101V            | Resistor, 100 Ω,<br>0.25W, 1206     | R7                                |

| 57    | 1 | Panasonic-ECG | ERO-S2PHF22R0           | Resistor, 22 Ω,                     | RLS                               |

www.irf.com - 9 -

|    |   |                   |                       | 0.25W, Axial                                     |          |

|----|---|-------------------|-----------------------|--------------------------------------------------|----------|

| 58 | 1 | Panasonic-ECG     | ERJ-P08J473V          | Resistor, 47 kΩ,<br>0.25W, 1206                  | R5       |

| 59 | 1 | Panasonic-ECG     | ERJ-P08J363V          | Resistor, 36 kΩ,<br>0.25W, 1206                  | RPH      |

| 60 | 1 | Panasonic-ECG     | ERJ-P08J471V          | Resistor, 470 Ω,<br>0.25W, 1206                  | R8       |

| 61 | 1 | Panasonic-ECG     | ERJ-P08J511V          | Resistor, 510 Ω,<br>0.25W, 1206                  | R13      |

| 62 | 2 | Panasonic-ECG     | ERJ-P08J104V          | Resistor, 100 kΩ,<br>0.25W, 1206                 | RS1, RS2 |

| 63 | 2 | Panasonic-ECG     | ERJ-P08J474V          | Resistor, 470 kΩ,<br>0.25W, 1206                 | R23, R24 |

| 64 | 1 | Panasonic-ECG     | ERO-S2PHF2203         | Resistor, 220 k $\Omega$ , 0.25W, Axial          | RDC      |

| 65 | 1 | Copal Electronics | CT-94EW203            | Potentiometer, $20 \text{ k}\Omega$ , top adjust | VR1      |

| 66 | 1 | Panasonic-ECG     | ERZ-V10D431           | Varistor, 275VAC, 10mm                           | RV1      |

| 67 | 1 | Phoenix Passive   | 5063FM1R000J12AF<br>X | Fusible Resistor, 1 $\Omega$                     | F1       |

| 68 | 1 | Wago              | 235 Series            | Connector, 5 Way                                 | P1       |

| 69 | 1 | Wago              | 234 Series            | Connector, 4 way                                 | P2       |

|    |   |                   |                       |                                                  |          |

Table 1: Bill of Materials. Lamp type: TL5/28W, Line Input Voltage: 90-305 VAC

<u>www.irf.com</u> - 10 -

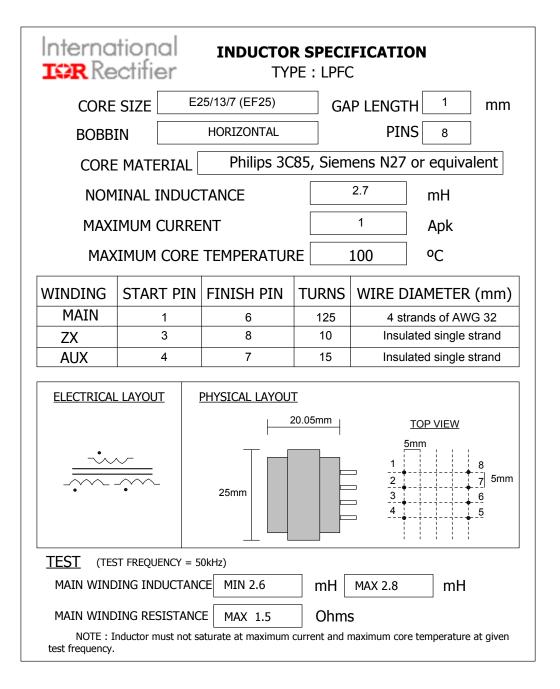

Fig. 4: Power Factor Inductor Specification

<u>www.irf.com</u> - 11 -

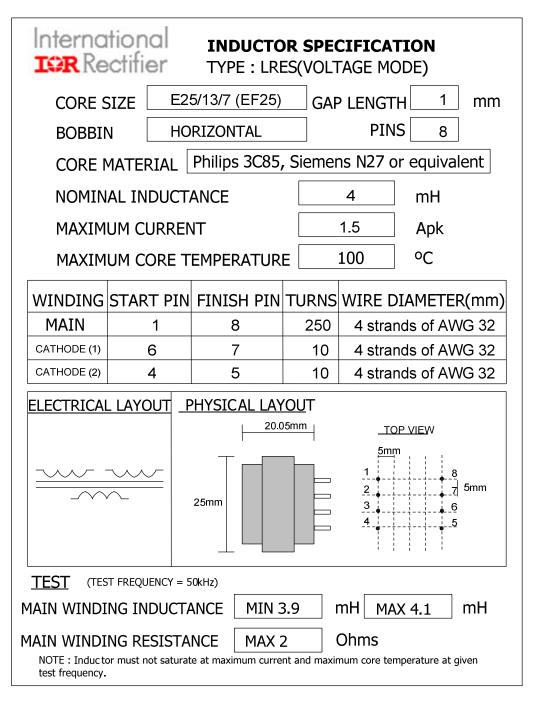

Fig. 5: Resonant Inductor Specification

www.irf.com - 12 -

# 8. Functional Description

The design of a dimmable ballast for linear lamps requires that the lamp power can be reduced smoothly to a low output level, less than 5% of nominal lumen output. It is necessary that the lamp output is able to be held at any level and that there will be no discernable flicker or instability at any level. In order to accomplish this, a closed loop control scheme is required. The fluorescent lamp represents a complex load, the impedance of which changes depending on the arc current and temperature of the gasses within the lamp. Like all discharge lamps, the fluorescent lamp displays a negative resistance behavior, meaning that as the current in the lamp increases the effective resistance of the lamp will reduce. The lamp impedance is strongly dependent on the arc current, however the relationship is not linear and temperature is also a factor.

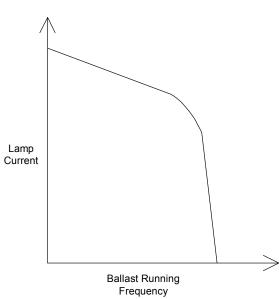

The IRPLDIM3 ballast as shown in the block diagram of Fig. 1 supplies the lamp through a resonant output circuit. In this design the lamp power is adjusted by changing the oscillation frequency of the MOSFET half bridge, which is driven by the IRS2158D. In this system the lamp current against ballast frequency characteristic of the system exhibits a sharp "knee" characteristic such that as the frequency increases the lamp current is gradually reduced up to a point at which a small increase of frequency will result in a large reduction in the lamp current.

Ballast / Lamp Operating Characteristic

Fig 6. Lamp Current against Ballast Frequency

Consequently it becomes necessary to include a stabilized closed loop feedback system to control the lamp current by adjusting the ballast frequency by means of a voltage controlled oscillator (VCO). In this example the VCO within the IRS2158D is driven by the output of an error amplifier and compensation network that senses the lamp arc current directly and compares it with a reference.

www.irf.com - 13 -

# Regulated Lamp Current Control System VCO & DRIVER Error Amplifier and Compensation Lamp Arc Current

#### Fig 7. Closed Loop Dimming Control

The isolated 0 to 10 V control interface operates by means of a simple circuit, described in <u>Design Tip DT-02</u>. This operates in the same way as many other commercially available 0 to 10 V dimming ballasts. The input internally biased at 10 V if nothing is connected and can be reduced to 0 V by sinking current only. Isolation between the dimming input and the ballast circuitry is provided by means of an optoisolator (IC4) and an additional isolated winding of the PFC boost inductor LPFC.

This winding must be isolated from the other two windings and from the ferrite cores and should be flash tested to 4 kV. In order to obtain sufficient voltage, this winding will need to have several more turns than the zero current detection winding. It is necessary to ensure that the voltage across the 18 V zener diode (D3) never falls below 18 V when the ballast output is dimmed and also over the range of line supply voltage. The next part of the circuit, centered around the *programmable unijunction transistor* Q1, generates an approximate ramp waveform across capacitor C7, which peaks at approximately 10 V guaranteeing maximum output when 10 V input is applied at the dimming input.

A trigger voltage provided by a potential divider of 9 V is applied to the gate of Q1. C7 charges through R15 until the voltage reaches a point one diode drop above the 9 V trigger voltage. Q1 then fires and remains switched on until the current drops below the valley current of the device which is small, discharging C7 again. This produces a continuously oscillating ramp waveform. It is important that R15 is sufficiently large that it does not supply a current larger than the valley current, otherwise Q1 remains on indefinitely and the circuit does not oscillate. It necessary for this oscillator to run at a frequency of several hundred Hz to prevent it from being a source of visible flicker.

This sawtooth signal is fed into the inverting input of a comparator. Note that this circuit makes use of a dual comparator IC by placing both comparators in parallel so as to provide greater current sinking capability to drive the input of IC4. However, there is no need for this provided the comparator used is capable of sinking the opto-isolator diode current, which in this case is around 13 mA. The opto-isolator diode current should be chosen to be as low as possible to guarantee saturation of the transistor when it sinks 1mA and consequently R14 is as large as possible. The non-inverting input is connected to the control input and pulled high via R20, which provides a sink current of 1 mA. C8 removes any noise that may be picked up at the comparator input.

The comparator output is open collector providing current to the input of IC4 when low. The diode will be continuously off when the input is at maximum and on when it is zero. Hence the opto-isolator output transistor will be fully on when the control voltage is at minimum and fully off when it is at maximum, providing a reasonably linear change in the duty cycle at intermediate levels. It is important in production to ensure that the opto-isolator used is rated to the correct voltage and has been certified to the necessary safety standards. The transistor side of the opto-isolator has the emitter connected to 0 V (COM) and the collector connected to the IRS2158D VCC supply of 15.6 V via a pull up resistor R22. The

<u>www.irf.com</u> - 14 -

collector node is then connected via R18 to CDIV and R19 to 0 V (COM). This averages the PWM signal and provides a DC reference to connect to the IRS2158D, which varies between 0V and the maximum voltage set. The range can be changed if necessary by adjusting the value of R19.

The value of the lamp current sensing resistor RLS will determine the feedback voltage provided to the op-amp feedback circuit of the IRS2158D. The value of RLS should be selected to provide as large a feedback as possible without dissipating too much power at maximum light output. It is recommended to keep the power dissipation in RLS below 0.25 W.

A delay is usually incorporated into dimming ballasts to provide a smooth fade from one dimming level to the next. For example, if the control inputs were to be shorted together, the lamp would fade down to minimum brightness over a period determined by the values used. This neatly avoids any flicker that may be caused by sudden changes in load in the PFC boost regulator section. In this case delay is provided via the time constant of R18 and CDIV. As the frequency of the PWM signal from the opto-isolator is of the order of tens of Hz, the delay has been designed to be long enough to ensure minimal ripple on the DC control voltage input to the IC. This can be increased if a longer fade time is desired by making CDIV larger.

Since the lamp arc current is being sensed with a resistor, it is necessary to use voltage mode preheating to avoid detecting the sum of the current in the arc added to the resonant output capacitor (CRES) current. This has an additional advantage that during preheat and prior to ignition of the lamp the arc current will always be zero and consequently the feedback circuit will not influence the oscillator frequency at all until the lamp is running. This means that by setting the value of RPH the preheat will occur in exactly the same way independent of the dimming control voltage achieving optimum preheat and ignition under all conditions.

#### Design of the Ballast

The initial step in designing the ballast is to determine values required for the resonant output inductor LRES and capacitor CRES. The *Ballast Design Assistant* (BDA) software, which can be downloaded from the International Rectifier web site, is an extremely useful tool in doing this. The BDA software used should be Version 4.2.x or above, this can be determined by clicking the Help button and clicking *About Ballast Designer*.

The following inputs were selected:

| IC            | IRS2158D                         |

|---------------|----------------------------------|

| Input         | 90 to 265VAC/500VDC              |

| Lamp          | T5 28W                           |

| Configuration | Single lamp/Voltage mode heating |

Table 2: Initial BDA inputs. Lamp type: TL5/28W, Line Input Voltage: 90-305 VAC

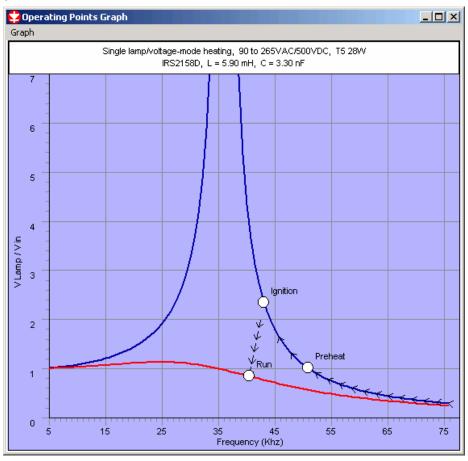

The next step is to click "Calculate". This displays the operating point for the ballast and calculates the values of the tank components, i.e. LRES = 5.9 mH and CRES = 3.3 nF.

<u>www.irf.com</u> - 15 -

Fig 8. Ideal Ballast Operating Points

The operating points here display an ideal condition where the ignition frequency is above the run frequency and the preheat frequency is somewhat higher than the ignition frequency. The run frequency also meets the target of 40 kHz. In general it is preferable to keep the run frequency (or minimum frequency) at 40 kHz or above to avoid possible interference with infra red remote controls, some of which operate at around 35 kHz.

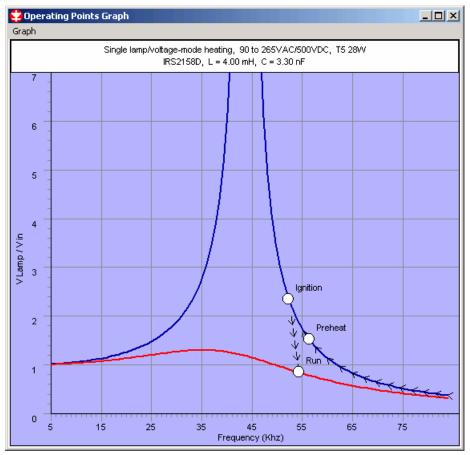

In order to use a more practical value, it was decided to fix LRES at 4 mH for this design, which is more easily available. In the BDA "Tank Components" section the "Fix L" box should be checked and the value of 4 mH entered in place of 5.9 mH. After the "Calculate" button has been clicked a message will appear stating that the ballast run frequency is now higher than the ignition frequency. Although many other ballast control IC's are not capable of operating under this set of conditions, the IRS2158D may be used without problems.

The graph for the operating points now looks like this:

<u>www.irf.com</u> - 16 -

Fig 9. Ballast Operating Points for IRPLDIM3

The operating points are as follows:

| Preheat Frequency   | 56.4 kHz |

|---------------------|----------|

| Ignition Frequency  | 52.3 kHz |

| Resonance Frequency | 43.8 kHz |

| Run Frequency       | 54.3 kHz |

Table 3: Practical Operating Points. Lamp type: TL5/28 W, Line Input Voltage: 90-305 VAC

In order to guarantee that the ballast is always capable of producing a high enough output voltage to ignite the lamp, the minimum frequency set by CT and RFMIN should be set close to the resonance frequency. If the minimum frequency is set too far above the resonance frequency, then during ignition the frequency will ramp down to the minimum frequency and remain there indefinitely. The ballast would not be able to operate correctly as it would never reach a low enough frequency to enable the ignition regulation to function, and would never produce enough voltage at the output, to ignite the lamp. In this design CT is 1 nF and RFMIN is  $15 \text{ k}\Omega$  giving a minimum frequency of approximately 40 kHz and a dead time of  $1.5 \text{ \mu}\text{s}$ , which are acceptable values.

The value of RPH sets the preheat frequency and has been selected at  $36~k\Omega$ . Since the minimum frequency is now below the run frequency, in order to prevent over driving the lamp, it is important to set the maximum lamp output. The operating range is defined by the values of RLS, R18 and R19. RLS is chosen to be as large as possible, to produce a sufficient feedback voltage, without dissipating too much power. A value of  $22~\Omega$  has been calculated to produce an average feedback voltage of 1.5~V when the lamp current is at its maximum value of 140~mA (RMS), with a power dissipation of 100~mW.

<u>www.irf.com</u> - 17 -

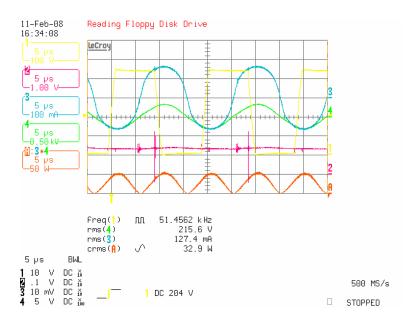

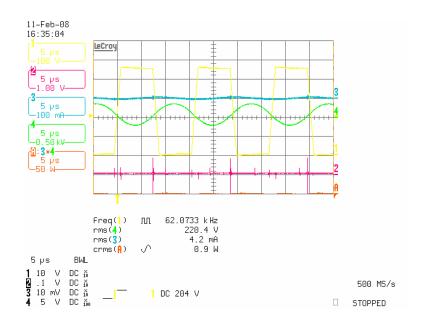

Fig 10. Ballast Waveforms at Maximum Brightness

| Trace | Color  | Signal                                    |

|-------|--------|-------------------------------------------|

| 1     | Yellow | Half Bridge Voltage – VS                  |

| 2     | Red    | Feedback Voltage at RLS (and DS1 Cathode) |

| 3     | Blue   | Lamp Arc Current                          |

| 4     | Green  | Lamp Voltage                              |

| A     | Orange | Lamp Power (3 multiplied by 4)            |

The values of R18 and R19 have been selected so that when the opto-isolator IC4 is completely off the voltage at the input of the error amplifier, at RDIM connection with the wiper of VR1, will be 1.5 V. This will set the error amplifier input voltage to 1.5 V when the 0 to 10 V dimming control voltage is a 10 V and maximum output is required. This effectively limits the maximum lamp power because the error amplifier will regulate the frequency in order to maintain equal voltage at RLS to the input voltage at RDIM. The run frequency will therefore be above the ignition frequency.

The minimum dimming level can be set by R19 and adjusted by RV1, which prevents the opto-isolator transistor from pulling the error amplifier input voltage all the way to zero. If the opto-isolator were on continuously the input voltage to the error amplifier would be so low that the lamp would extinguish or enter an unstable state of partial ignition. Tests have indicated that the T5 lamp behaves differently when cold and hot at very low light levels. When the lamp is cold the arc tends to become unstable as the lamp repeatedly extinguishes and re-ignites, however when the lamp is hot it is possible to dim all the way down to virtually zero output and a state can be observed where the lamp is in a stable state of semi ignition, characterized by an faint emission of light along only part of the length of the tube.

In a practical design it is desirable to limit the minimum output level to the minimum current at which the lamp can maintain stable operation when cold.

<u>www.irf.com</u> - 18 -

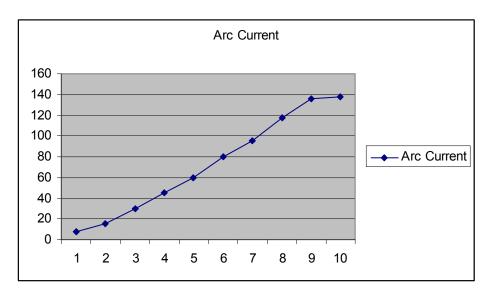

The ballast was measured over the input dimming range:

| Control   | Frequency | Ballast   | Lamp    | Arc Current | Arc Power | RLS      |

|-----------|-----------|-----------|---------|-------------|-----------|----------|

| Input (V) | (kHz)     | Power (W) | Voltage | (mA rms)    | (W rms)   | Feedback |

|           |           |           | (V rms) |             |           | Voltage  |

| 1         | 57.0      | 14.6      | 190     | 8           | 1.5       | 0.07     |

| 2         | 55.7      | 15.5      | 201     | 15          | 3.5       | 0.15     |

| 3         | 55.4      | 18.6      | 200     | 30          | 7.0       | 0.30     |

| 4         | 55.2      | 21.3      | 195     | 45          | 10.0      | 0.45     |

| 5         | 55.0      | 23.7      | 187     | 60          | 12.0      | 0.60     |

| 6         | 54.0      | 26.0      | 180     | 80          | 15.0      | 0.80     |

| 7         | 52.8      | 28.5      | 173     | 95          | 19.0      | 0.90     |

| 8         | 51.5      | 31.0      | 167     | 118         | 22.0      | 1.15     |

| 9         | 49.0      | 33.4      | 162     | 136         | 25.5      | 1.37     |

| 10        | 48.7      | 33.5      | 161     | 138         | 26.2      | 1.40     |

**Table 4: Dimming Test Results**

These are average values as there is some frequency modulation occurring at all times as the system regulates and compensates for impedance changes in the lamp.

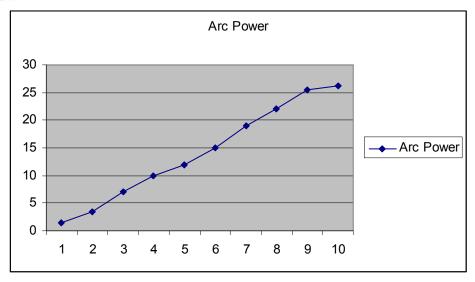

The measured results show that the lamp arc current and power are reasonably linear with respect to the input control voltage:

Fig 11. Graph of lamp arc current against control voltage input

<u>www.irf.com</u>

Fig 12. Graph of lamp arc power against control voltage input

Fig 13. Ballast Waveforms at Minimum Brightness

#### **Power Factor Correction Section**

The power factor correction stage at the front end of the ballast is based on a standard critical conduction mode circuit using an industry standard control IC. This stage has been designed to provide a DC bus of 480 V and operates with the AC line input voltage from 90 Vrms up to 305 Vrms, which is the maximum voltage that may occur on a 277 VAC line, allowing virtually world wide operation.

The value of LPFC given by the BDA software is 2.7 mH. In a dimming design with a wide voltage input range it is necessary to select the optimum value for the PFC inductor.

<u>www.irf.com</u> - 20 -

The inductance must be sufficiently large to allow the PFC controller IC1 to maintain stable operation when the line input at maximum and the dimming level is at minimum. Under these conditions the COMP voltage at pin 2 will be very low and the PWM on time will be very short. If the inductor value is too small the on time will become too small for the control IC to be able to maintain a stable DC bus.

The result of an unstable DC bus is a slight but visible flicker seen when the lamp is dimmed. Such instability is usually caused by instability of the power factor correction section rather than the lamp current regulation loop incorporated within the IRS2158D (IC2).

The trade off is that if the value of LPFC is too high the bus voltage will start to drop at low line input and maximum load since the COMP pin voltage has reached maximum and therefore the maximum on time limit has been reached. The lamp current control loop is however able to lower the ballast frequency in order to compensate for this to some degree if necessary.

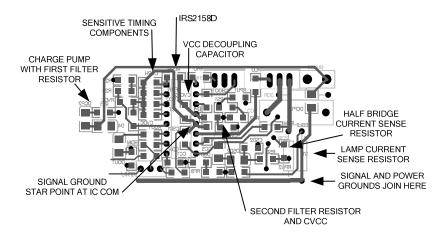

#### **PCB Layout Considerations**

In order to successfully utilize the IRS2158D in a ballast design, it is necessary to follow the following PCB layout guidelines. This can avoid possible interference and ground loop issues that can occur in the ballast circuit. These connection techniques also prevent high current ground loops from interfering with sensitive timing component operation, and allows the entire control circuit to reject common-mode noise due to output switching.

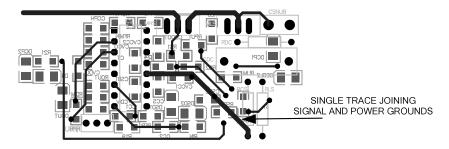

Figure 14 and Figure 15 show the control section of a typical ballast designed around the IRS2158D, where the IC is located in the center. In this design all SMD devices are mounted under the PCB with discrete devices on top.

Fig 14. Critical traces on the bottom side of the PCB

Fig 15. Critical traces on the top side of the PCB

<u>www.irf.com</u> - 21 -

- 1. The signal ground (pin 12) should only be connected to the power ground at one single point to prevent ground loops from forming.

- 2. The point described in (1) should be where the grounds of the current sense resistors for both the half bridge MOSFETs and the lamp current feedback both meet.

- 3. The VCC decoupling capacitor should be placed as close to the IRS2158D VCC (pin 13) and COM (pin 12) as possible with the shortest possible traces.

- 4. The devices; CPH, RMIN, CVCO, CT and CCS should all be located as close to the IRS2158D as possible with traces to the relevant pins being as short as possible.

- 5. The ground connections from the devices listed in (4) should be connected back to the COM pin of the IRS2158D through the shortest possible traces. These should be connected back to the COM pin of the IC without joining the power ground trace at any point. In the example shown above the power ground trace runs along the lower side of the board on the bottom Copper layer

- 6. The charge pump diode connection to ground should be made to the power ground not the signal ground.

- 7. The power factor correction section (if used) should be kept apart from the ballast control as shown in the example above, the power factor correction section is at the left side of the PCB.

#### **Output Inductor Design**

The output inductor LRES should be designed to allow a sufficient peak ignition current without saturating. This is important as the ballast will be unable to ignite if unable to deliver sufficient voltage at the lamp. The ignition current depends on the type of lamp being used and must be kept to a minimum by ensuring that the cathodes are sufficiently preheated. To minimize eddy current losses in the inductor windings multi-stranded wire should be used. Ferrite cores of sufficiently good quality should also be used to allow a high peak flux density at increased temperature and low core losses. It is important to have a large enough air gap to produce the highest available peak current before allowing the inductor to saturate. If the air gap is too large however, losses can occur because the magnetic field emanating from the gap extends far enough to induce eddy currents in the windings.

When the cores are hot the saturation point and hence the peak current for the inductor will be lower therefore a poorly designed inductor may result in the ballast failing to ignite the lamp during an attempted hot re-strike.

The inductor design process can be greatly simplified by using the Ballast Designer software. For this application it is recommended to fix the core size to EF25 and gap size at 1mm.

#### **Lamp Preheating**

It is essential that the lamp be sufficiently preheated before ignition. The correct preheat current can be determined from published data or from International Rectifier's Ballast Designer software.

It is necessary in order to achieve the maximum possible lamp life to heat the cathodes to the correct temperature before ignition. Accelerated deterioration occurs if lamps are ignited when the cathodes are either not sufficiently heated or over heated. The cathode temperature at ignition is determined by the preheat current, which in turn is determined by the preheat frequency through RPH and the preheat time set by CCPH.

#### Cathode heating after ignition (Run mode)

The lamp filament (Cathode) resistance over the range of dimming levels should be between 3 and 5.5 times the resistance when cold. A simple method for determining the hot resistance is to first connect one cathode to a DC power supply via an ammeter and slowly increase the voltage from zero, noting the current at 1 V intervals. This should be done until the cathode can be seen to be glowing red. When this occurs the voltage should not be increased further or the cathode is likely to overheat and become open circuit. With these results, the resistance can be calculated for each voltage and hence the acceptable

<u>www.irf.com</u> - 22 -

voltage range can be found to comply within the 3 to 5.5 times cold resistance limits. The cold resistance can be easily measured with a digital multi-meter (DMM).

When the ballast is running, a true RMS digital voltmeter or differential oscilloscope probe can be connected across the lower cathode and the voltage can be observed at maximum and minimum brightness. The cathode voltage normally increases as the ballast is dimmed. The values of COUT1 and COUT2 plus the resonant output inductor heater windings will control how much. Reducing the capacitance will reduce the amount by which the voltage rises. The COUT1 and COUT2 values should be chosen to prevent the voltage exceeding the upper limit at minimum output to prevent premature end blackening of the lamps and reduced life.

Note that utilizing additional windings on the inductor to provide cathode heating means that power is transferred through the core and consequently the core losses will increase and hence the core operating temperature. The core will reach its highest operating temperature when the ballast is running at minimum brightness.

The component values in this design have been selected for a 28W T5 linear lamp. The circuit will need to be optimized for the particular lamp used to obtain best performance.

#### Ignition

The IRS2158D incorporates regulated ignition control.

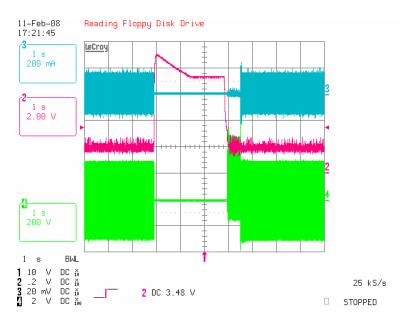

Fig 16. Lamp Voltage and CPH pin voltage - No Ignition

At the end of the preheat period the IRS2158D VCO pin voltage increases and so the frequency decreases until the voltage at the CS pin reaches the internal threshold of 1.25 V. At this point the IRS2158D internally pulls down the VCO pin voltage and therefore regulates the circulating current in the resonant output circuit of the ballast and maintains a constant voltage across the lamp (green trace). This voltage will remain while the CPH pin voltage (red trace) charges from 1/3VCC to 1/2VCC. If the lamp has not ignited at this point the IRS2158D will shut down. If preheat is insufficient the ballast will fail to ignite and shut down at the end of the ignition phase as shown in *Fig 16*. In this design the ignition voltage has been set at 1.25 kV peak and 2 kV peak to peak. This ignition voltage is correct for worst case conditions in a 28W TL5 lamp and can be set by using an RCS value of 1.5R.

A good lamp normally ignites as the output voltage ramps up to the ignition regulation level as shown in Fig 17.

<u>www.irf.com</u> - 23 -

Fig 17. Lamp Voltage and Current – Correct Ignition

#### **Protection Circuits**

The SD pin of the IRS2158D is used for lamp removal protection. If there is no lamp present the voltage at SD pin will be pulled above the 5 V threshold via RPU1 and RPU2 and RSD charging CSD1 and CSD2 through DSD1 and DSD2. When a lamp is in circuit the voltage at the junction of RPU2 and RSD will be held low via DS1 and RLS. In this way when a lamp is removed the ballast shuts down and the lamp is replaced with a good one the ballast starts up again. In the IRPLDIM3 design the pull up of the SD pin for lamp removal detection is connected to the DC bus instead of VCC as in some other designs. This is because an additional 12 V zener diode DSD2 has been added, so that any voltage at the lower cathode produced during preheat, which can contain some DC offset will never be sufficient to falsely trip the lamp removal shut down circuit. In addition to this pulling up through resistors to the DC bus provides a more rapid response without draining current from VCC and maintains the SD pin voltage firmly above the 5 V threshold when no lamp is present under all conditions of line input voltage.

During preheat and ignition modes the end of life protection function, which monitors the lamp voltage through the SD pin is not enabled, therefore the ballast will operate as long as the SD pin remains below 5 V. The SD pin is normally biased at 2 V from an internal voltage source within the IRS2158D.

<u>www.irf.com</u> - 24 -

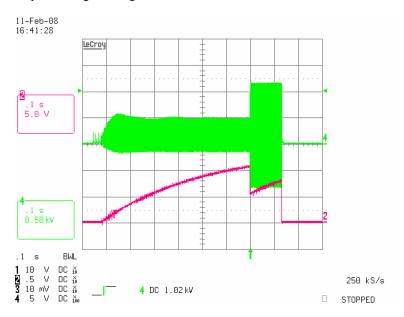

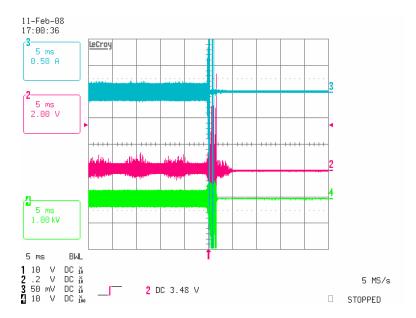

Fig 18. Lamp removal and replacement

| Trace | Color | Signal           |

|-------|-------|------------------|

| 2     | Red   | SD Pin Voltage   |

| 3     | Blue  | Lamp Arc Current |

| 4     | Green | Lamp Voltage     |

The VDC pin of the IRS2158D (IC2) is also connected to the DC bus through the divider formed by R23 and R24, with CVDC to COM to remove ripple and noise. This provides brown out protection for the ballast which works by sensing the rectified AC line voltage at the positive output of BR1. When the VDC voltage falls below 3 V the IRS2158D shuts down. The values of R23 and R24 are selected so that this condition occurs when the AC line input drops below the minimum level at which the ballast can maintain sufficient DC bus voltage for the lamp to remain ignited and run at the correct power. When the ballast has shut down the voltage at the VDC pin will rise because the voltage at BR1 will no longer be full wave rectified as there is no load and C2 is sufficient to maintain a DC level. To prevent the ballast from immediately re-starting there is a 2 V hysteresis such that the VDC pin must rise above 5 V in order for the IRS2158D to restart. This will only happen after the AC line has been restored to a sufficient level.

Without the brownout protection provided by the VDC pin if a brownout did occur the ballast would shut down in the event of any hard switching at VS because voltage spikes would appear at the CS pin. This would cause the fault counter to count up until the ballast shut down. In that event the ballast would shut down and remain off until the line is switched off and then back on again. This is undesirable and with the implementation of the VDC pin of the IR2158D can easily be avoided so that the ballast will automatically recover from a Brownout event and switch the light back on.

<u>www.irf.com</u> - 25 -

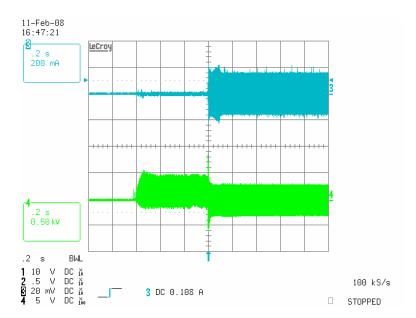

Fig 19. Brownout shutdown and restart

| Trace | Color | Signal           |

|-------|-------|------------------|

| 2     | Red   | VDC Pin Voltage  |

| 3     | Blue  | Lamp Arc Current |

| 4     | Green | Lamp Voltage     |

The IRPLDIM3 ballast also includes end of life protection, which is enabled only after successful ignition when the ballast is in run mode. The lamp voltage is divided down through REOL1, REOL2, REOL3 and REOL4. This divided voltage is fed to two back to back zener diodes, DEOL1 (7.5 V) and DEOL2 (5.1 V). The SD pin is internally biased at 2 V with a window comparator that has 1 V and 3 V thresholds. If the positive peak of the lamp voltage becomes large enough to allow DEOL1 to reverse breakdown then the SD pin voltage will rise above 3 V. A delay is incorporated by clocking the oscillator pulses with the fault counter so that after a number of cycles the IRS2158D will shut down. The delay is normally around 1ms and was added to provide some immunity to transients and false shutting down of the end of life circuit. In the same way if the negative peak of the lamp voltage drops low enough for DEOL2 to reverse breakdown then the SD pin will fall below 1 V. After the same delay period the IRS2158D will also shut down. This end of life circuit will therefore cause the ballast to shut down if an aging lamp is connected if it produces an asymmetric voltage in either direction, due to the rectifying effect. End of lamp life shutdown is often a mandatory requirement for electronic ballasts.

In the event of a ballast output becoming open circuit during running, for example if the lamp is broken or cracked but the filament is still intact, the SD pin will not detect a fault. However the ballast will still shut down because the CS pin will detect the transients caused by hard switching of the half bridge MOSFETs. In this case the fault counter will be active so that approximately 60 consecutive transients need to be detected by the CS pin before shut down. The *broken lamp test* is easily simulated by disconnecting the high voltage end of the lamp during running, which is the end that is not connected to the SD pin lamp out detection circuit.

<u>www.irf.com</u> - 26 -

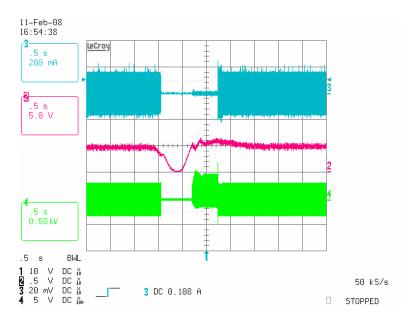

Fig 20. Broken Lamp Test

| Trace | Color | Signal           |

|-------|-------|------------------|

| 2     | Red   | CS Pin Voltage   |

| 3     | Blue  | Lamp Arc Current |

| 4     | Green | Lamp Voltage     |

The above waveforms illustrate the delay of approximately 1ms introduced by the fault counter. This avoids any possibility of false tripping occurring if random transients occur.

#### Disclaimer

This reference design kit is intended for evaluation purposes only and has not been submitted or approved by any external test house for conformance with UL or international safety or performance standards. International Rectifier does not guarantee that this reference design will conform to any such standards.

Ballast Designer software may be downloaded free of charge from: <a href="https://www.irf.com/whats-new/nr051026.html">www.irf.com/whats-new/nr051026.html</a>

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105

Data and specifications subject to change without notice. 3/13/2008

<u>www.irf.com</u> - 27 -